Imec представи транзистори от следващо поколение – те са бързи, ефективни и достъпни за производство

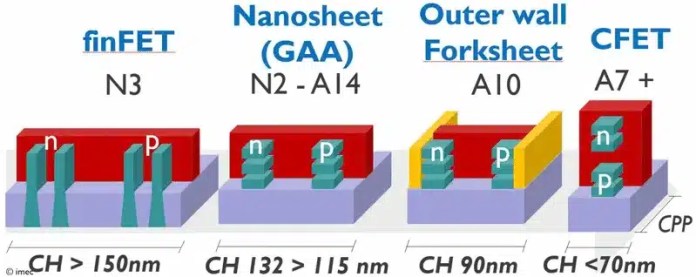

Преди около 6 години белгийският център Imec представи напълно нова транзисторна архитектура – CFET (complementary FETs). Тя трябваше да помогне за производството на транзистори със скорост на производство под 2 nm. Архитектурата се характеризира с отделни канали за наностепенно захранване (forksheet). Технологията обаче се оказа трудна за производство, затова Imec създаде модифицирана междинна версия на бъдещата архитектура, която беше представена преди няколко дни.

Същността на архитектурата forksheet се състои в разделяне на GAA транзисторите от n- и p-тип с диелектрична преграда.

Преградата или стената е проектирана така, че да сведе до минимум влиянието на съседните транзистори един върху друг. В този случай двойка транзистори с различна проводимост могат да бъдат изработени на по-малка площ на чипа, което води до значително намаляване на площта на чипа с до 20 %. Нещо повече, Imec предлага да се поставят транзистори един върху друг, за да се реализира архитектурата CFET, което допълнително ще намали площта на чипа. Последвалата работа по транзисторите с разделени страници обаче показа, че идеята за диелектрична преграда е изключително трудна за реализиране в производството.

Най-тънката диелектрична преграда с дебелина от 8 до 10 nm трябваше да бъде произведена първа, дори преди всички манипулации с кристалите и ецването на транзисторите. Не всеки материал може да издържи на такова „малтретиране“, което би довело до високо ниво на дефекти. Тогава Imec предложи гениално решение – преградите трябва да са външни. Те вече не дистанцират многополюсните транзистори един от друг, а изолират двойки транзистори от съседните двойки. Всъщност това представлява изолиране на транзистори с еднаква проводимост.

С този процес преградите се превръщаха в едни от последните на кристала. Това решение позволява използването на познати материали. Поради по-дебелите стени площта на транзисторните двойки можеше да бъде леко засегната, но всички останали предимства под формата на повишена скорост (токове) и намалено изтичане се запазиха. По-тънкият преход между наностените и външната стена позволи на гейта да покрие увеличена площ на ръба на всяка наностена, което значително подобри контрола на токовете на транзисторните канали.

И накрая, окончателното изработване на външните стени около транзисторните канали увеличи механичното напрежение в нановлакната (в транзисторните канали). Терминът „напрегнат силиций“ е познат на всеки, който се занимава с производство на чипове от поне четвърт век. При такива условия проводимостта се увеличава.

Разработчиците признават, че с увеличаването на дебелината на външните изолационни прегради между транзисторите до 15 nm общата площ на чипа може да бъде малко по-голяма, отколкото в случай на използване на вътрешни прегради, но това е малка и необходима жертва. CAD моделирането на SRAM клетки и осцилатори, използващи транзистори с нанолистове с външни прегради, показа, че при статичните клетки памет новата схема за технологичния процес А10 (10 Angstrom) намалява площта с 22% в сравнение с нанолистовете А14 без изолация, което се дължи на по-плътното пакетиране на еднотипните устройства и намалената стъпка на гейта.

За осцилаторни схеми с пълно натоварване новата схема съответства или надвишава производителността на осцилаторите за технологични процеси A14 и 2 nm. При празен товар захранващият ток е намален с около 33% (намаляване на утечките).

Опитът в производството на разделени наностабилни транзистори ще бъде важен за разработването на CFET, тъй като много технологични стъпки, материали и концепции за проектиране ще се припокриват. Във forksheet транзисторите устройствата от p-тип и n-тип се поставят едно до друго. За разлика от тях, в следващото поколение CFET двата различни типа транзистори ще бъдат разположени вертикално, въпреки че основната технология ще остане същата, но това е история от средата на 30-те години на миналия век, към която ще се връщаме многократно в бъдеще.