Renesas представи собствено 32-битово RISC-V ядро

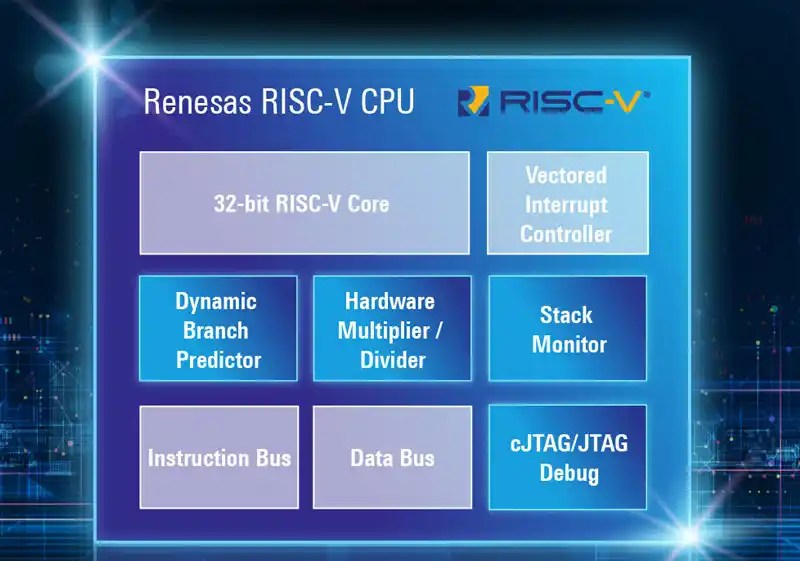

Renesas Electronics обяви собствено 32-битово процесорно ядро, базирано на архитектурата с отворен код RISC-V (ISA) със собствени инструкции. Решението ще допълни съществуващата фамилия 32-битови микроконтролери (MCU) на Renesas, включително патентованите продукти RX и RA на базата на архитектурата Arm Cortex-M.

RISC-V ядрото на Renesas е предназначено за създаване на чипове с общо предназначение. Очаква се този тип процесори да намерят приложение в устройствата за интернет на нещата, потребителската електроника, медицинското оборудване, промишлените системи и т.н.

Новото ядро може да служи като основен контролер за приложения или като допълнителен вторичен модул в едночиповите системи (SoC). Освен това ядрото е подходящо за вградени в чипа най-разнообразни подсистеми и специфични за конкретното приложение продукти (ASSP). Производителността е оценена на 3,27 CoreMark/MHz, което според Renesas превъзхожда почти всички други подобни решения на пазара.

Ядрото на компанията Renesas реализира някои разширения на RISC-V ISA: това са M (умножение/деление на цели числа), A (атомни операции с паметта), C (компресиран формат на инструкциите; подмножество на RV32I) и B (инструкциите за работа с битове). Renesas планира да представи първия си MCU, базиран на RISC-V, и свързаните с него инструменти за разработка през първото тримесечие на 2024 г. Техническите подробности за продукта ще бъдат публикувани по същото време.