TSMC разкри кога ще започне да произвежда 1,4 nm чипове с нанолистове

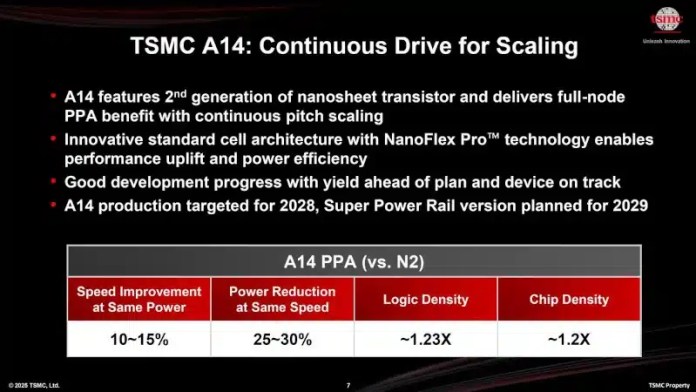

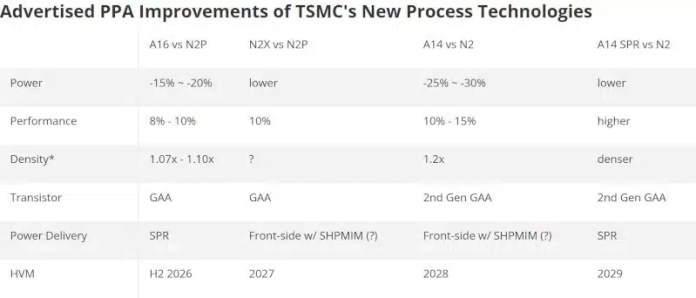

TSMC обяви 1,4-нанометровият процес A14 за Gate-All-Around (GAA) транзистори от второ поколение. Технологията ще осигури 10-15% увеличение на производителността при същата консумация на енергия и 25-30% намаление на консумацията на енергия при запазване на честотата и логическата сложност в сравнение с 2nm N2. Плътността на логическите елементи ще се увеличи с 23%, а общата плътност на транзисторите ще се увеличи с 20% в среда на смесен дизайн. Масовото производство е планирано за 2028 година, като през 2029 година ще дебютира версия на чипа със задно захранване.

По време на Северноамериканския технологичен симпозиум TSMC заяви, че A14 е нов процес, разработен от нулата, така че проектите на чипове, проектирани за предишни технологични процеси няма да са подходящи за него.

Новият процес е изграден на базата на второ поколение нанолистови транзистори (нанолистове), произведени по най-новата технология GAA. Това го отличава от процеса N2P, базиран на платформата N2, и от A16, който е подобрен N2P с Backside Power Delivery (BSPDN). За разлика от A16, базовата версия на A14 не поддържа архитектурата Super Power Rail. Това намалява разходите, но ограничава приложението на технологията в сценарии, при които се изисква захранващо окабеляване с висока плътност. Липсата на BSPDN обаче прави A14 жизнеспособен избор за приложения, при които ползите от тази технология са минимални или не съществуват.

Въпреки липсата на BSPDN, процесът A14 поддържа висока ефективност чрез използване на второ поколение транзистори с нанолистове. Един от ключовите компоненти на технологията е NanoFlex Pro – усъвършенствана архитектура на стандартните клетки, която дава на проектантите гъвкавост при конфигурирането на логическите блокове въз основа на три важни показателя: производителност, консумация на енергия и площ на чипа (Power, Performance, Area – PPA). Въпреки че компанията не разкрива техническите разлики между NanoFlex Pro и предишната версия на NanoFlex, може да се предположи, че те включват разширени възможности за DTCO – съвместна оптимизация на дизайна и технологиите – както и по-фина настройка на ниво клетка и транзистор.

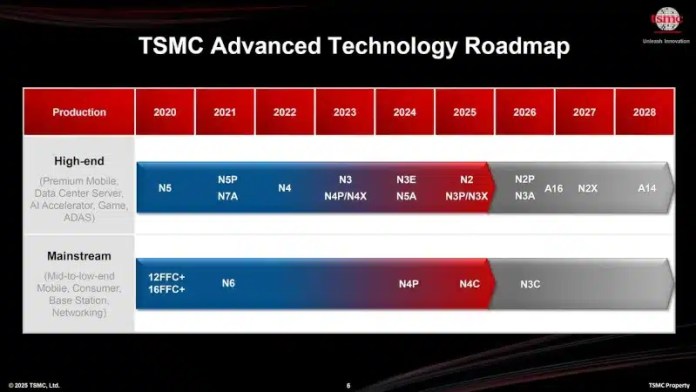

TSMC очаква масовото производство на чипове с технология A14 да започне през 2028 година. В същото време компанията все още не е уточнила през кое полугодие ще започне масовото производство на тези чипове.

Като се има предвид, че масовото производство на технологичните процеси N2P и A16 ще започне през втората половина на 2026 година, може да се предположи, че производството на чипове по технология A14 ще бъде насрочено за първата половина на 2028 година. През 2029 година се очаква версия на A14 с архитектура Super Power Rail (SPR) – система за доставка на енергия от задната страна на чипа (BSPDN). Въпреки че официалното име на тази модификация все още не е обявено, тя вероятно ще следва приетата от TSMC номенклатура и ще бъде обозначена като A14P.

A14 разполага със система за подаване на енергия от предната страна, подобна на тази, използвана в технологичните процеси N2 и N2P. Това прави архитектурата особено подходяща за клиентски и специализирани компютърни приложения, които не изискват оформление на захранващи линии с висока плътност, но при които енергийната ефективност и мащабируемостта са от решаващо значение.

Според TSMC процесът A14 е насочен към широк спектър от приложения, включително клиентски устройства и крайни изчислителни задачи, при които е важна високата производителност при ограничения на мощността и площта на матрицата. Чрез архитектурни характеристики и параметри технологията A14 осигурява баланс по ключови показатели на PPA в различни сценарии за проектиране.