TSMC ще произвежда гигантски чипове, 40 пъти по-бързи от днешните

Размерите на съвременните процесори обикновено са малки, но най-големият производител на полупроводници в света TSMC разработва нов вариант на своята технология за опаковане на чипове CoWoS, която може да се използва за създаване на структури с размери до 9,5 фотомаски (7885 mm²) върху пластини с размери 120 × 150 mm (18 000 mm²).

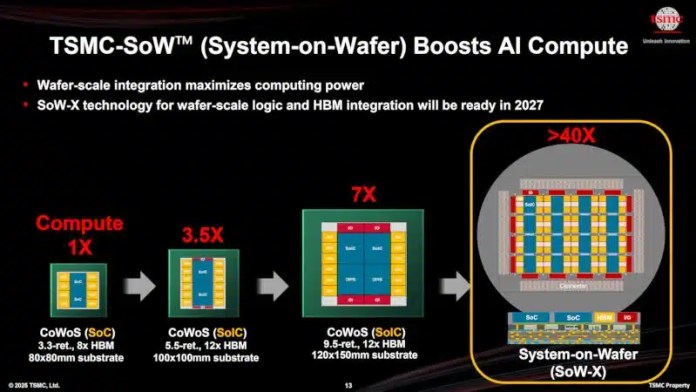

Производителността на такива гигантски чипове ще бъде 40 пъти по-висока от тази на днешните процесори – но това не е пределът.

Почти всички съвременни високопроизводителни процесори, предназначени за центрове за данни вече са многочипови. С нарастването на търсенето на по-бързи решения разработчиците се стремят да интегрират още повече силиций в своите системи. В стремежа си да отговори на това търсене TSMC разширява възможностите си за опаковане на чипове и ги прави още по-големи. На събитието си North American Technology Symposium компанията показа своята пътна карта за 3DFabric: междинните слоеве ще нараснат далеч отвъд възможностите на настоящата технология.

Настоящата версия на технологията за опаковане CoWoS на TSMC позволява да се използват междинни слоеве с размер до 2831 mm² – три пъти по-голям от размера на фотомаската: стандартът за екстремна ултравиолетова литография (EUV) е 858 mm², докато TSMC използва 830 mm². ИИ-ускорителите AMD Instinct MI300X и NVIDIA B200 с два големи логически чипа и осем стека HBM3 или HBM3E памет вече са достигнали тази граница.

Това обаче вече не е достатъчно за бъдещите процесори. Догодина или малко по-късно TSMC ще представи нова технология за опаковане CoWoS-L, която поддържа междинни слоеве с площ до 4719 mm² – това е около 5,5 пъти повече от площта на стандартна фотомаска. Такива опаковки ще включват до 12 стека памет и ще изискват по-голяма пластина с размери 100 × 100 mm (10 000 mm²). Решенията, изградени на базата на такава архитектура ще позволят три пъти по-висока изчислителна производителност от сегашните проекти. Това ще е достатъчно например за ускорителите NVIDIA Rubin с 12 стека HBM4, но в бъдеще ще е необходима по-голяма мощност.

В бъдеще TSMC възнамерява да предлага на клиентите си междинни слоеве с площ до 7885 mm² – 9,5 пъти повече от максималната възможна фотомаска, разположени върху пластина с размери 120 × 150 mm.

За сравнение, стандартният размер на кутията за компактдискове е приблизително 125 × 142 mm. Миналата година компанията говореше за многочипови конструкции с размери 120 × 120 mm (около осем пъти по-големи от фотомаската) и изглежда, че ръстът на този показател отразява търсенето на клиентите. Такъв дизайн би включвал четири компонента с вертикално разположение на SoIC кристали (например кристал N2 или A16 върху логика N3), 12 стека HBM4 и допълнителни I/O кристали.

TSMC има клиенти, които искат най-високата възможна производителност и са готови да платят за нея. За тях компанията предлага технологията System-on-Wafer (SoW) – производство на чипове с размера на силициева пластина.

Досега само Cerebras и Tesla са се възползвали от тази възможност, но TSMC е уверена, че и други клиенти ще се присъединят към тях. Актуализираната технология SoW-X, базирана на CoWoS ще позволи създаването на многочипови ИИ-ускорители с размер на силициева пластина, върху които могат да се инсталират HBM памет и оптични връзки. Предвижда се SoW-X да бъде представена през 2027 година.

Процесори с размер на маската 9,5 пъти по-големи от максималната възможна фотомаска или дори с размер на пластина изискват значителни усилия при производството и сглобяването. Един от основните проблеми е захранването: такива чипове изискват киловатна мощност и силен ток. За производителите на сървъри става все по-трудно да решат този проблем самостоятелно, така че той ще трябва да се решава на системно ниво. TSMC предлага да интегрира монолитни интегрални схеми за управление на захранването (PMIC) с вертикални връзки „от край до край“ (TSV), изработени с технологията N16 FinFET, и индуктори, монтирани на подложката в CoWoS-L пакети с RDL (Redistribution Layer) интерпозитори. Това ще позволи захранването да се насочи през пластината, като се намали разстоянието между захранващите устройства и активните кристали, което от своя страна ще намали паразитното съпротивление и ще подобри целостта на захранването в системата.

PMIC, произведени по технологията N16 позволяват по-прецизен контрол на подаването на енергия към процесорите, твърдят от TSMC. Това е особено важно при многоядрени и многочипови проекти, при които работните натоварвания могат да се променят бързо, но трябва да се поддържа стабилна производителност на системата. Схемата осигурява прецизна настройка с динамично скалиране на напрежението (DVS) при дадено количество ток. В сравнение с традиционните подходи плътността на мощността се увеличава пет пъти.

Подходът на TSMC отразява промяната към оптимизация на системно ниво: доставката на енергия вече се разглежда като неразделна част от силиция, опаковката и цялостния дизайн, а не като отделна функция на всеки компонент.

Увеличаването на размера на междинния модул ще има отражение върху дизайна на системата – особено по отношение на форм-фактора на опаковката. Подложката с размери 100 × 100 mm е почти на границата на формата OAM 2.0 (102 × 165 mm). Бъдещата подложка с размери 120 × 150 mm вече я надвишава и вероятно ще трябва да се въведат нови стандарти за опаковане на модули и оформление на платки. Освен това подобни системи „система в опаковка“ (SiP) генерират огромно количество топлина. За да се справят с този проблем, производителите вече проучват нови методи за охлаждане, включително директно течно охлаждане, което NVIDIA използва в своите GB200/GB300 NVL72, както и технологии за потапяне, които да помогнат за справяне с топлината, генерирана от многокиловатовите процесори, а това е предизвикателство, което TSMC няма да може да реши на ниво чип или SiP – поне засега.