До 2029 г. TSMC ще започне да произвежда чипове по 1,2 nm и 1,3 nm технологичен процес с настоящото оборудване

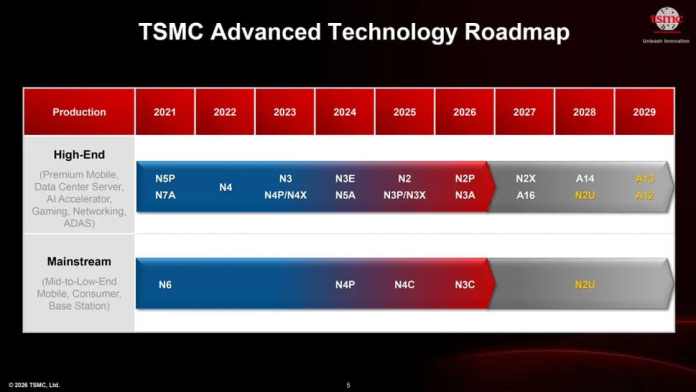

Тайванският гигант TSMC представи актуализирана пътна карта за полупроводниковите технологии до 2029 г. на Северноамериканския технологичен симпозиум. Акцентът беше поставен върху новите технологии от клас 1,2nm и 1,3nm – A12 и A13, както и върху 2nm решения. Пускането на A16, чийто клиент трябваше да бъде Nvidia, беше отложено за 2027 г. Освен това TSMC умишлено се отказа от използването на свръхскъпите High-NA EUV литографи през следващите няколко години, като предпочете да увеличи мащаба на настоящите решения.

Един от основните анонси беше процесът A13, който ще бъде еволюция на A14 и ще бъде пуснат през 2029 г. Както и при по-ранния 2nm процес, A13 ще запази транзисторите от типа GAA – компанията залага на постепенното мащабиране без резки технологични скокове, което намалява рисковете по отношение на сроковете и добива на добри кристали. Новият процес ще осигури 6% увеличение на плътността на транзисторите чрез оптично намаляване на размера, като същевременно ще запази съвместимостта със съществуващите стандарти за проектиране и електрически параметри. Това ще позволи на клиентите да се възползват от по-високата плътност на транзисторите с минимално препроектиране.

Успоредно с това компанията разширява линията си от 2 nm решения с новия възел N2U. Той ще бъде третото поколение на платформата N2 и ще осигури 3-4% увеличение на производителността или 8-10% намаление на консумацията на енергия, без да се преминава към изцяло нова архитектура. Това е особено важно за производителите на потребителска електроника, където разходите и повторното използване на IP -блоковете играят ключова роля.

TSMC също така преминава към разделена стратегия за разработване на технологичните процеси. Сега компанията ще пуска нови възли ежегодно за потребителски устройства като смартфони и на всеки две години за взискателни приложения, включително изкуствен интелект и високопроизводителни изчисления. Този подход отразява промяната на пазара: докато преди мобилните устройства бяха основният двигател на приходите, сега двигателите на растежа са изкуственият интелект и центровете за данни.

За тези приложения TSMC разработва отделна линия от технологии, включително A16 и предстоящия A12. Те са фокусирани върху максимизиране на производителността и използват архитектура със захранване от задната страна (Super Power Rail), за да подобрят ефективността и плътността на транзисторите. Масовото производство на A16 се очаква през 2027 г., а A12 ще бъде следващата стъпка през 2029 г.

TSMC разработва и решения за опаковане. Технологията CoWoS (Chip-on-Wafer-on-Substrate) ще позволи до 2028 г. в един чип да се комбинират до десет изчислителни кристала и до 20 стека HBM памет. За 3D интеграцията компанията подготвя актуализирана версия на SoIC (System on Integrated Chips): до 2029 г. плътността на взаимовръзките ще се увеличи около 1,8 пъти, което ще осигури по-плътно свързване на кристалите и по-бърз обмен на данни. Новият продукт ще бъде съвместим с технологични процеси от ниво А14.

Интересно е, че не се планира технологичните технологии A13 и A12 да използват High-NA EUV литография поне до 2029 г. Цената на един такъв скенер от ASML може да достигне 350-380 млн. долара. За разлика от Intel, който разчита на тази технология, TSMC предпочита да се възползва максимално от настоящите EUV решения, избягвайки високите разходи за ново оборудване. Компанията подчертава, че тази стратегия вече дава резултати: инженерите продължават да намират начини за увеличаване на мащаба, без да преминават към по-скъпи технологии.

Всичко важно от света на технологиите, директно в пощата ти.

Всичко важно от света на технологиите, директно в пощата ти.

С абонирането приемате нашите Условия и Политика за поверителност. Може да се отпишете с един клик по всяко време.