AI агент проектира напълно функционален RISC-V процесор за 12 часа, въз основа на заявка от 219 думи

Стартъпът за проектиране на чипове с помощта на изкуствен интелект Verkor.io обяви, че неговата агентна система Design Conductor е създала самостоятелно напълно функционално ядро на RISC-V процесор. Системата е взела документ с изисквания с обем 219 думи и за 12 часа е генерирала верифициран проект, готов за производство. Това е с порядъци по-бързо от стандартните 18–36 месеца, които обикновено отнема търговската разработка на чипове.

Според Verkor, това е първият случай, в който автономен агент е създал работещ процесор. Последният, наречен VerCore представлява ядро с 5-степенен конвейер, последователно изпълнение и един поток от команди. Той достигна тактова честота от 1,48 GHz при технологичния процес ASAP7 (7 nm) и постигна 3261 точки в теста CoreMark.

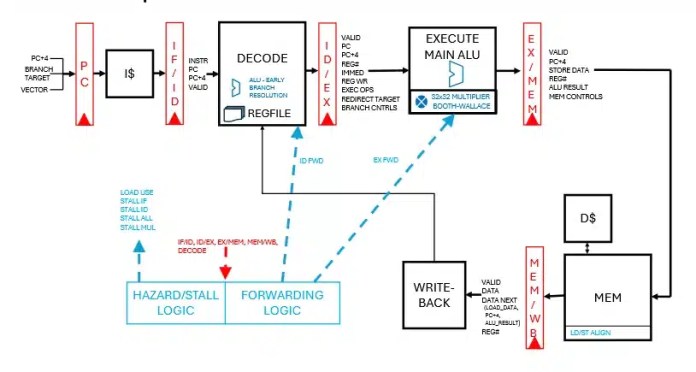

В документа на Verkor подробно се описва архитектурата на конвейера, включваща етапите на извличане, декодиране, изпълнение, достъп до паметта и обратно записване, с ранно разрешаване на разклоненията и препращане на операнди. В хода на оптимизацията системата самостоятелно реализира бърз умножител на Бут-Уолъс с честота 2,57 GHz и избра конструкция с наказание за разклонение в един такт след тестване на варианти с един и два такта. Производителността на VerCore се сравнява с Intel Celeron SU2300, мобилен чип от 2011 година, базиран на архитектурата Penryn.

5-степенно ядро без кеш и извънредно изпълнение e доста проста конструкция по индустриални стандарти. В самата статия на Verkor се отбелязва, че разработката на авангардни чипове струва над 400 милиона долара и отнема 18–36 месеца с участието на стотици инженери. VerCore е много по-прост, но 12-часовият срок все пак е забележителен за напълно автономна работа от началото до края, дори ако на това относително ниско ниво на сложност са били необходими „много десетки милиарди токени“.

VerCore не е бил физически изработен и е бил тестван единствено в симулация с помощта на Spike (еталонният ISA RISC-V симулатор). ASAP7 е академичен набор от инструменти за проектиране, а не производствен 7 nm технологичен процес. Verkor твърди, че в симулацията може да стартира версия на uCLinux.

Авторите на работата честно признават ограниченията на големите езикови модели: AI агентът понякога „подценява сложността на работата, необходима за решаване на определени проблеми“. Например, при нарушаване на временните характеристики Design Conductor се опита да „задълбочи конвейера“ радикално, вместо да търси по-прости решения.

В друг случай AI моделът разсъждаваше за Verilog (език за описание на хардуера, управляван от събития) така, сякаш това беше последователен код. Изследователите изчислиха, че за да се доведе системата до чип, готов за производство, все още ще са необходими от 5 до 10 експерти-хора. Освен това изискванията към изчислителната мощност нарастват нелинейно с увеличаването на сложността на проекта, което прави процеса по-малко практичен в търговски мащаби. Verkor планира да пусне изходния код на VerCore (RTL) и скриптовете за компилиране до края на април, както и да демонстрира реализацията на FPGA на конференцията DAC.

Всичко важно от света на технологиите, директно в пощата ти.

Всичко важно от света на технологиите, директно в пощата ти.

С абонирането приемате нашите Условия и Политика за поверителност. Може да се отпишете с един клик по всяко време.