Samsung изпревари конкуренцията с първия в индустрията по-тънък от 10 nm чип за DRAM памет

Като най-голям производител на памети южнокорейската компания Samsung Electronics се опитва своевременно да премине към по-съвършени литографски стандарти, тъй като това намалява разходите за производство на памети в дългосрочен план. Наскоро компанията представи първия работещ DRAM кристал, произведен по технология, по-тънка от 10 nm.

Традиционно литографските норми в областта на производството на чипове за памет изостават от тези в областта на логическите компоненти, тъй като в първия случай усъвършенстваните технологии просто не са необходими и не се оправдават. Така или иначе, доскоро производителите на памети активно овладяваха процесите от 10 nm клас, които бяха подредени в следната последователност: 1x, 1y, 1z, 1a, 1b, 1c и 1d (в низходящ ред на геометричните параметри). Samsung наскоро получи първия работен образец на DRAM кристал, произведен с помощта на процеса от поколение 10а, който поставя началото на ерата на литографските стандарти, по-тънки от 10 nm, в производството на памет. Линейните размери в този случай варират от 9,5 nm до 9,7 nm, както уточнява The Elec.

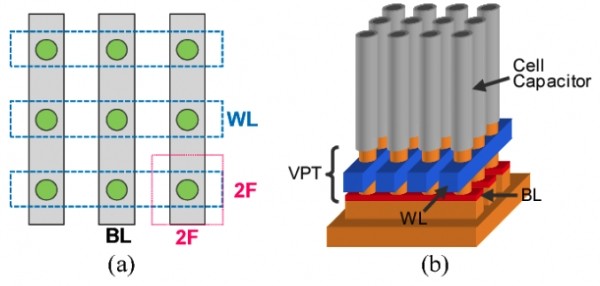

Следващите етапи на внедряване на този процес предполагат началото на използването му в масовото производство на чипове памет през 2028 г. Трите последователни технологии (10a, 10b и 10c) ще включват използването на архитектура на клетките 4F2 и транзистори с вертикален канал (VCT). В последващата технология 10d компанията ще премине към 3D DRAM. Samsung се е застраховала в случай, че 10a се провали в масовото производство, като паралелно разработва алтернативни технологии, но получаването на работещи образци я обнадеждава, че основният сценарий ще проработи.

Въвеждането на 10а крие рискове за Samsung, свързани с увеличаването на плътността на клетките памет. Структурата 4F2 предполага 30-50% увеличение на броя на клетките на единица площ от кристала. В същото време транзисторите с вертикален канал (VCT) позволяват кондензаторът да бъде поставен над транзистора, което също увеличава плътността на клетките в чипа. Периферните вериги ще бъдат изготвяни на отделен чип и монтирани под основния чип, като се използва хибриден метод за свързване на пластините. Промените в оформлението са довели и до промяна в химическия състав на елементите. Вместо от силиций, Samsung ще направи транзисторните канали от индиев, галиев и цинков оксид (IGZO), за да потисне токовете на утечка и да осигури по-стабилно съхранение на данни в по-компактни клетки памет.

При избора на материал за линията на управление Samsung разглежда две алтернативи: титанов нитрид и молибден, но последният е силно корозивен и изисква въвеждането на ново оборудване, така че везните все още не са се наклонили към конкретен вариант. Вертикалните канали в транзисторите, според експертите, са първата стъпка към 3D DRAM, така че Samsung се движи към тази технология по еволюционен път. В същото време Micron Technology и китайските производители на памет ще заобиколят етапа на 4F2 и VCT, като очакват да преминат направо към 3D DRAM.

Триизмерната подредба, наред с другото, ще позволи производството на памет с по-висока плътност без използването на свръхтвърда ултравиолетова литография (EUV), която изисква по-скъпо оборудване. За китайските производители това е двойно по-важно, като се има предвид липсата на достъп до такова оборудване в условията на западните санкции. Корейската SK hynix, следвайки примера на Samsung, възнамерява да използва 4F2 и VCT, но само в рамките на процеса 10b, а не 10a.

Всичко важно от света на технологиите, директно в пощата ти.

Всичко важно от света на технологиите, директно в пощата ти.

С абонирането приемате нашите Условия и Политика за поверителност. Може да се отпишете с един клик по всяко време.